Verilog 实现101序列检测器——Moore和Mealy型状态机实现可重叠和不可重叠_摩尔型和米利型的 verilog-程序员宅基地

技术标签: Verilog实验

1. 可重叠和不可重叠区分

- 可重叠的序列检测器检测到一个目标串后可以不用回到初始状态,该目标串的元素的可作为下一个目标串的子串继续进行判断。

0 1 1 0 1 0 1 0 1 1 1 0 - 不可重叠的序列检测器一次检测完成后必须回到初始状态。

0 1 1 0 1 0 1 0 1 1 1 0

| 输入 | 0 | 1 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 可重叠检测输出 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 0 |

| 不可重叠检测输出 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

2. 可重叠序列检测器实现

2.1. 米利机

- 输出由当前状态和输入共同决定

module mealy_overlap (

output reg dout,

input wire clk,

input wire rst,

input wire din

);

reg [1:0] curr_state;

reg [1:0] next_state;

parameter IDLE = 2'b 00;

parameter S1 = 2'b 01;

parameter S2 = 2'b 10;

always @ (posedge clk or negedge rst) begin

if (!rst) begin

curr_state <= IDLE;

end else begin

curr_state <= next_state;

end

end

always @ (*) begin

case (curr_state)

IDLE: begin

if (din == 1) begin next_state <= S1; dout <= 0; end

else begin next_state <= IDLE; dout <= 0; end

end

S1: begin

if (din == 0) begin next_state <= S2; dout <= 0; end

else begin next_state <= S1; dout <= 0; end

end

S2: begin

if (din == 1) begin next_state <= S1; dout <= 1; end

else begin next_state <= IDLE; dout <= 0; end

end

default: begin next_state <= IDLE; dout <= 0; end

endcase

end

endmodule

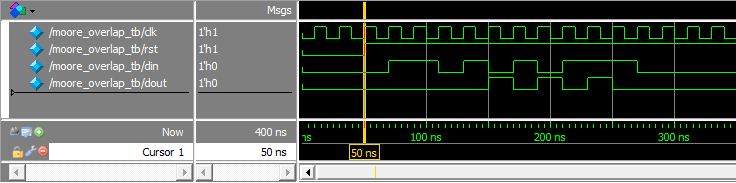

2.2. 摩尔机

- 输出由当前状态决定

module moore_overlap (

output reg dout,

input wire clk,

input wire rst,

input wire din

);

reg [1:0] curr_state;

reg [1:0] next_state;

parameter IDLE = 2'b 00;

parameter S1 = 2'b 01;

parameter S2 = 2'b 10;

parameter S3 = 2'b 11;

always@ (posedge clk or negedge rst) begin

if (!rst) begin

curr_state <= IDLE;

end else begin

curr_state <= next_state;

end

end

always @ (*) begin

case (curr_state)

IDLE: begin

if (din == 1) next_state <= S1;

else next_state <= IDLE;

end

S1: begin

if (din == 0) next_state <= S2;

else next_state <= S1;

end

S2: begin

if (din == 1) next_state <= S3;

else next_state <= IDLE;

end

S3: begin

if (din == 1) next_state <= S1;

else next_state <= S2;

end

default: begin next_state <= IDLE;

end

endcase

end

always @ (*) begin

if (curr_state == S3) dout <= 1;

else dout <= 0;

end

endmodule

3. 不可重叠序列检测器实现

3.1. 米利机

module mealy_not_overlap (

output reg dout,

input wire clk,

input wire rst,

input wire din

);

reg [1:0] curr_state;

reg [1:0] next_state;

parameter IDLE = 2'b 00;

parameter S1 = 2'b 01;

parameter S2 = 2'b 10;

always @ (posedge clk or negedge rst) begin

if (!rst) begin

curr_state <= IDLE;

end else begin

curr_state <= next_state;

end

end

always @ (*) begin

case (curr_state)

IDLE: begin

if (din == 1) begin next_state <= S1; dout <= 0; end

else begin next_state <= IDLE; dout <= 0; end

end

S1: begin

if (din == 0) begin next_state <= S2; dout <= 0; end

else begin next_state <= S1; dout <= 0; end

end

S2: begin

if (din == 1) begin next_state <= IDLE; dout <= 1; end

else begin next_state <= IDLE; dout <= 0; end

end

default: begin next_state <= IDLE; dout <= 0; end

endcase

end

endmodule

3.2. 摩尔机

module moore_not_overlap (

output reg dout,

input wire clk,

input wire rst,

input wire din

);

reg [1:0] curr_state;

reg [1:0] next_state;

parameter IDLE = 2'b 00;

parameter S1 = 2'b 01;

parameter S2 = 2'b 10;

parameter S3 = 2'b 11;

always@ (posedge clk or negedge rst) begin

if (!rst) begin

curr_state <= IDLE;

end else begin

curr_state <= next_state;

end

end

always @ (*) begin

case (curr_state)

IDLE: begin

if (din == 1) next_state <= S1;

else next_state <= IDLE;

end

S1: begin

if (din == 0) next_state <= S2;

else next_state <= S1;

end

S2: begin

if (din == 1) next_state <= S3;

else next_state <= IDLE;

end

S3: begin

if (din == 1) next_state <= S1;

else next_state <= IDLE;

end

default: begin next_state <= IDLE;

end

endcase

end

always @ (*) begin

if (curr_state == S3) dout <= 1;

else dout <= 0;

end

endmodule

摩尔机和米利机的区别

Moore状态机的输出仅依赖于当前状态而与输入无关。想要输出dout = 1,状态S3必须形成。

Mealy状态机的输出与当前状态和输入有关。想要输出dout = 1,状态S2下输入din = 1就可以了,不需要状态S3。根据波形可对比反应更快。

智能推荐

GIS二次开发(C++):矢量缓冲区分析 GDAL/QGIS开发包_c++ gis开发包-程序员宅基地

文章浏览阅读636次,点赞12次,收藏10次。上述代码只能获取当前地图中的第一个图层作为缓冲区分析的数据源,不支持选择图层。_c++ gis开发包

ECharts折线图渲染速度变慢、ECharts折线图数据为0时不显示线条_echarts 折现图 值为0-程序员宅基地

文章浏览阅读6.4k次,点赞9次,收藏26次。写在前面:在公司做一个大屏可视化项目时,遇到了这样的需求:1.使折线图渲染速度变慢;2.当折线图数据为0时不显示线条本文就拿ECharts给的示例做演示。示例代码如下:import * as echarts from 'echarts';var chartDom = document.getElementById('main');var myChart = echarts.init(chartDom, 'dark');var option;option = { xAxi._echarts 折现图 值为0

React监听窗口变化_react 监听控制台打开关闭变化-程序员宅基地

文章浏览阅读8.8k次。React组件监听窗口变化基本思路:改变事件方法中的this指向constructor(props) { this.resizeBind = this.resizeTTY.bind(this)}添加监听componentDidMount() { window.addEventListener('resize', this.resizeBind)}注销事件compone..._react 监听控制台打开关闭变化

硬件测试入门-聊一聊示波器的带宽_示器的带宽-程序员宅基地

文章浏览阅读1.8k次,点赞8次,收藏31次。带宽通常为示波器的第一指标,也是我们在选择示波器时首要考虑的因素。信号经过探头进入示波器后,首先经过的就是放大器和衰减器,它们决定了示波器的带宽大小,在没有特别说明的情况下我们说的带宽是示波器模拟前端放大器的带宽,也就是-3dB截止点。_示器的带宽

Total Variation loss-程序员宅基地

文章浏览阅读653次。图像上的一点点噪声可能就会对复原的结果产生非常大的影响,很多复原算法都会放大噪声。因此需要在最优化问题的模型中添加一些正则项来保持图像的光滑性,图片中相邻像素值的差异可以通过降低TV loss来一定程度上解决,比如降噪,对抗checkerboard等等。受噪声污染的图像的总变分比无噪图像的总变分明显的大,最小化TV理论上就可以最小化噪声。总变分定义为梯度幅值的积分。即:求每一个像素和横向下一个像素的差的平方,加上纵向下一个像素的差的平方。_total variation loss

1.自动化上线代码-分布式版本控制系统Git_系统功能分布式上线-程序员宅基地

文章浏览阅读414次。01.自动化上线代码基本介绍01.自动化上线代码基本介绍1.CI/CD基础概念1.1 软件开发生命周期1.2 什么是环境1.3 什么是代码部署1.4 代码发布的方式1.4.1 手动发布1.4.2 自动发布2.什么是持续集成2.1 什么是集成2.2 什么是持续集成2.3 持续集成的好处2.4 持续集成的目的3.什么是持续交付4.什么是持续部署5.完整代码发布流程02.分布式版本控制系统Git._系统功能分布式上线

随便推点

Python元类是怎么创建一个类的?-程序员宅基地

文章浏览阅读331次,点赞5次,收藏3次。new。

QT:等待对话框_qt等待对话框-程序员宅基地

文章浏览阅读967次。1. gif动图显示等待对话框#include "waitting.h"#include "ui_waitting.h"Waitting::Waitting(QWidget *parent) : QWidget(parent), ui(new Ui::Waitting){ ui->setupUi(this); this->setWindowOpacity(0.8); setWindowFlags(Qt::Dialog | Qt::Frame_qt等待对话框

新手探索NLP(十五)——终章_nlp constraint-程序员宅基地

文章浏览阅读335次。目录中文语音的机器处理汉语语言学的研究未登录词识别概率图模型信息熵互信息联合熵条件熵统计语言模型隐马尔科夫模型Viterbi算法最大熵模型最大熵原理GIS实现条件随机场模型概念:线性链条件随机场不同模型的比较与总结词性、语块和命名实体识别词性语块命名实体识别句法理论和自动分析理论基础句法分析..._nlp constraint

电脑怎么用计算机打开指令,win10如何打开计算器工具 快速打开Win10计算器的四种方法...-程序员宅基地

文章浏览阅读602次。最近,有位windows10用户反映自己在写“电脑配置”相关文章的时候,常常需要使用到计算器工具。可是每次在Win10系统中找计算器工具都要找很久。这该怎么办呢?接下来,小编就向大家分享四种快速打开Win10计算器的方法。方法一:使用组合快捷键1、同时按下Win+R组合快捷键打开运行操作框,然后在打开后面输入命令:Calc.exe,如下图。2、然后点击底部的确定,就可以快速打开Win10计算器了。..._win10计算器快捷键

Excel 单元格自定义格式,输入ddd.mmss格式的度分秒,转化显示成ddd mm ss格式_dd.mmss是什么格式-程序员宅基地

文章浏览阅读1.6k次,点赞2次,收藏2次。Excel 单元格自定义格式,输入ddd.mmss格式的度分秒,显示成ddd mm ss格式测绘中常用到的角度记录格式即为ddd.mmss,常用于电子经纬仪数据导出以及测量计算软件的数据导入,如何利用excel表格实现这一格式的数据显示呢?如下图设置单元格格式即可。”0”:数字占位符。如果单元格的内容大于占位符,则显示实际数字,如果小于点位符的数量,则用0补足。“#”:数字占位符。只显有意义的零而不显示无意义的零。小数点后数字如大于”#”的数量,则按”#”的位数四舍五入。“?”:数字占位符。在小_dd.mmss是什么格式

企业微信跳转链接,跳转到默认浏览器打开_企业微信#target=out-程序员宅基地

文章浏览阅读2.6w次,点赞2次,收藏7次。在链接上最后,加上:“#target=out” 参数即可跳转至电脑默认的浏览器。_企业微信#target=out