TestBench 基本写法与框架-程序员宅基地

技术标签: FPGA

Verilog硬件描述语言在数字电路的设计中使用的非常普遍,无论是哪种语言,仿真都是必不可少的。而且随着设计复杂度的提高,仿真工具的重要性就越来越凸显出来。在一些小的设计中,用TestBench来进行仿真是一个很不错的选择。VHDL与Verilog语言的语法规则不同,它们的TestBench的具体写法也不同,但是应包含的基本结构大体相似,在VHDL的仿真文件中应包含以下几点:实体和结构体声明、信号声明、顶层设计实例化、提供激励;Verilog的仿真文件应包括:模块声明、信号声明、顶层设计实例化、提供激励。大致思想都是相似的。

简单的说,TestBench就是一种验证手段,从软件层面对设计的硬件电路进行仿真。具体来讲,一般是在你的仿真文件里,产生激励信号,作用于被仿真的设计文件DUT(Design Under Test),产生相应的输出,然后根据输出信号检验设计的电路是否存在问题或者存在哪些问题。

下面以FPGA板中驱动流水灯的一段程序为例,简单介绍一下两种语言的TestBench的编写。

1 module led_run(clk,rst,led); 2 input clk,rst; 3 output reg [7:0] led; 4 reg [25:0] clk_cnt; 5 reg clk_tmp; 6 reg [3:0] temp; 7 8 always@(posedge clk or negedge rst) 9 begin 10 if(!rst) 11 begin 12 clk_cnt<=26'd0; 13 clk_tmp<=1'b1; 14 end 15 else 16 begin 17 if(clk_cnt==26'b11111111111111111111111111) 18 begin 19 clk_cnt<=26'd0; 20 clk_tmp<=~clk_tmp; 21 end 22 else 23 clk_cnt<=clk_cnt+1'b1; 24 end 25 end 26 27 always@(posedge clk_tmp or negedge rst) 28 begin 29 if(!rst) 30 temp<=4'd15; 31 else 32 temp<=temp+1'b1; 33 end 34 35 always@(temp) 36 begin 37 case(temp) 38 4'd0 :led<=8'b11111110; 39 4'd1 :led<=8'b11111100; 40 4'd2 :led<=8'b11111000; 41 4'd3 :led<=8'b11110000; 42 4'd4 :led<=8'b11100000; 43 4'd5 :led<=8'b11000000; 44 4'd6 :led<=8'b10000000; 45 4'd7 :led<=8'b00000000; 46 4'd8 :led<=8'b00000001; 47 4'd9 :led<=8'b00000011; 48 4'd10:led<=8'b00000111; 49 4'd11:led<=8'b00001111; 50 4'd12:led<=8'b00011111; 51 4'd13:led<=8'b00111111; 52 4'd14:led<=8'b01111111; 53 4'd15:led<=8'b11111111; 54 default:; 55 endcase 56 end 57 58 endmodule

上面是一段流水灯的代码,控制8位流水灯依次点亮,再依次熄灭。第一个always语句完成分频功能,第二个always语句用于计数,共16个值,第三个always语句根据计数的值选择LED灯的状态。其中clk、rst分别为时钟和复位信号,led为驱动流水灯的输出信号。接下来针对这一设计编写其TestBench文件。

1 /************TestBench*************/ 2 module tb_led_run; 3 reg clk,rst; 4 wire led; 5 6 initial 7 begin 8 rst=1; 9 #30 rst=0; 10 #40 rst=1; 11 end 12 13 initial 14 begin 15 clk=1; 16 forever #20 clk=~clk; 17 end 18 19 led_run led1(.clk(clk),.rst(rst),.led(led)); 20 endmodule

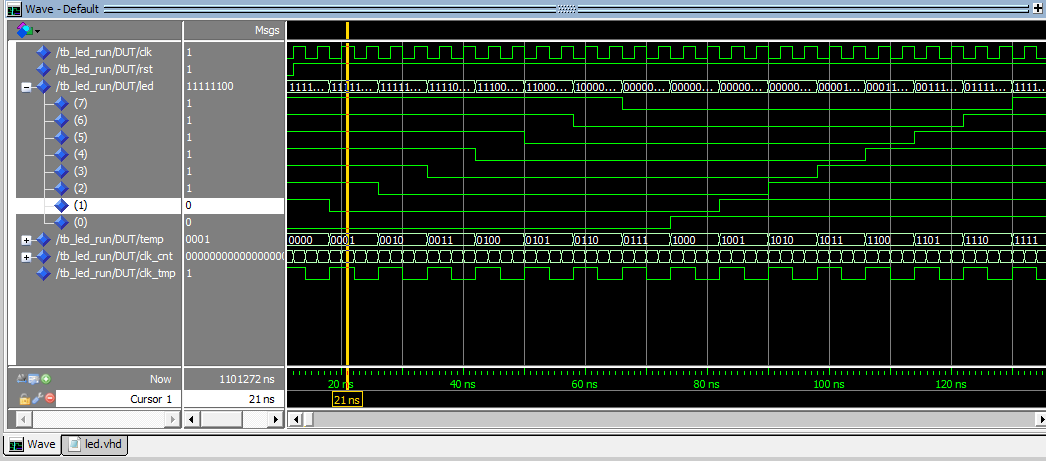

由于只需要时钟和复位信号即可,故在其仿真文件并不复杂,建立测试模块,进行信号声明,在两个initial中分别提供clk和rst信号,最后进行例化。当然注意一点,在仿真时要把分频模块去掉,或者将分频系数改小,否则仿真时不容易观察波形。下面是在Modelsim中仿真得到的波形(分频模块改为2分频)。

总结起来,Verilog的TestBench有着相对固定的写法:

module test_bench;

端口声明语句

initial

begin

产生时钟信号

end

initial

begin

提供激励源

end

例化语句

endmodule

最主要的是在initial语句中进行激励的生成,这要根据具体的设计来分析。

智能推荐

FTP命令字和返回码_ftp 登录返回230-程序员宅基地

文章浏览阅读3.5k次,点赞2次,收藏13次。为了从FTP服务器下载文件,需要要实现一个简单的FTP客户端。FTP(文件传输协议) 是 TCP/IP 协议组中的应用层协议。FTP协议使用字符串格式命令字,每条命令都是一行字符串,以“\r\n”结尾。客户端发送格式是:命令+空格+参数+"\r\n"的格式服务器返回格式是以:状态码+空格+提示字符串+"\r\n"的格式,代码只要解析状态码就可以了。读写文件需要登陆服务器,特殊用..._ftp 登录返回230

centos7安装rabbitmq3.6.5_centos7 安装rabbitmq3.6.5-程序员宅基地

文章浏览阅读648次。前提:systemctl stop firewalld 关闭防火墙关闭selinux查看getenforce临时关闭setenforce 0永久关闭sed-i'/SELINUX/s/enforcing/disabled/'/etc/selinux/configselinux的三种模式enforcing:强制模式,SELinux 运作中,且已经正确的开始限制..._centos7 安装rabbitmq3.6.5

idea导入android工程,idea怎样导入Android studio 项目?-程序员宅基地

文章浏览阅读5.8k次。满意答案s55f2avsx2017.09.05采纳率:46%等级:12已帮助:5646人新版Android Studio/IntelliJ IDEA可以直接导入eclipse项目,不再推荐使用eclipse导出gradle的方式2启动Android Studio/IntelliJ IDEA,选择 import project3选择eclipse 项目4选择 create project f..._android studio 项目导入idea 看不懂安卓项目

浅谈AI大模型技术:概念、发展和应用_ai大模型应用开发-程序员宅基地

文章浏览阅读860次,点赞2次,收藏6次。AI大模型技术已经在自然语言处理、计算机视觉、多模态交互等领域取得了显著的进展和成果,同时也引发了一系列新的挑战和问题,如数据质量、计算效率、知识可解释性、安全可靠性等。城市运维涉及到多个方面,如交通管理、环境监测、公共安全、社会治理等,它们需要处理和分析大量的多模态数据,如图像、视频、语音、文本等,并根据不同的场景和需求,提供合适的决策和响应。知识搜索有多种形式,如语义搜索、对话搜索、图像搜索、视频搜索等,它们可以根据用户的输入和意图,从海量的数据源中检索出最相关的信息,并以友好的方式呈现给用户。_ai大模型应用开发

非常详细的阻抗测试基础知识_阻抗实部和虚部-程序员宅基地

文章浏览阅读8.2k次,点赞12次,收藏121次。为什么要测量阻抗呢?阻抗能代表什么?阻抗测量的注意事项... ...很多人可能会带着一系列的问题来阅读本文。不管是数字电路工程师还是射频工程师,都在关注各类器件的阻抗,本文非常值得一读。全文13000多字,认真读完大概需要2小时。一、阻抗测试基本概念阻抗定义:阻抗是元器件或电路对周期的交流信号的总的反作用。AC 交流测试信号 (幅度和频率)。包括实部和虚部。图1 阻抗的定义阻抗是评测电路、元件以及制作元件材料的重要参数。那么什么是阻抗呢?让我们先来看一下阻抗的定义。首先阻抗是一个矢量。通常,阻抗是_阻抗实部和虚部

小学生python游戏编程arcade----基本知识1_arcade语言 like-程序员宅基地

文章浏览阅读955次。前面章节分享试用了pyzero,pygame但随着想增加更丰富的游戏内容,好多还要进行自己编写类,从今天开始解绍一个新的python游戏库arcade模块。通过此次的《连连看》游戏实现,让我对swing的相关知识有了进一步的了解,对java这门语言也有了比以前更深刻的认识。java的一些基本语法,比如数据类型、运算符、程序流程控制和数组等,理解更加透彻。java最核心的核心就是面向对象思想,对于这一个概念,终于悟到了一些。_arcade语言 like

随便推点

【增强版短视频去水印源码】去水印微信小程序+去水印软件源码_去水印机要增强版-程序员宅基地

文章浏览阅读1.1k次。源码简介与安装说明:2021增强版短视频去水印源码 去水印微信小程序源码网站 去水印软件源码安装环境(需要材料):备案域名–服务器安装宝塔-安装 Nginx 或者 Apachephp5.6 以上-安装 sg11 插件小程序已自带解析接口,支持全网主流短视频平台,搭建好了就能用注:接口是公益的,那么多人用解析慢是肯定的,前段和后端源码已经打包,上传服务器之后在配置文件修改数据库密码。然后输入自己的域名,进入后台,创建小程序,输入自己的小程序配置即可安装说明:上传源码,修改data/_去水印机要增强版

verilog进阶语法-触发器原语_fdre #(.init(1'b0) // initial value of register (1-程序员宅基地

文章浏览阅读557次。1. 触发器是FPGA存储数据的基本单元2. 触发器作为时序逻辑的基本元件,官方提供了丰富的配置方式,以适应各种可能的应用场景。_fdre #(.init(1'b0) // initial value of register (1'b0 or 1'b1) ) fdce_osc (

嵌入式面试/笔试C相关总结_嵌入式面试笔试c语言知识点-程序员宅基地

文章浏览阅读560次。本该是不同编译器结果不同,但是尝试了g++ msvc都是先计算c,再计算b,最后得到a+b+c是经过赋值以后的b和c参与计算而不是6。由上表可知,将q复制到p数组可以表示为:*p++=*q++,*优先级高,先取到对应q数组的值,然后两个++都是在后面,该行运算完后执行++。在电脑端编译完后会分为text data bss三种,其中text为可执行程序,data为初始化过的ro+rw变量,bss为未初始化或初始化为0变量。_嵌入式面试笔试c语言知识点

57 Things I've Learned Founding 3 Tech Companies_mature-程序员宅基地

文章浏览阅读2.3k次。57 Things I've Learned Founding 3 Tech CompaniesJason Goldberg, Betashop | Oct. 29, 2010, 1:29 PMI’ve been founding andhelping run techn_mature

一个脚本搞定文件合并去重,大数据处理,可以合并几个G以上的文件_python 超大文本合并-程序员宅基地

文章浏览阅读1.9k次。问题:先讲下需求,有若干个文本文件(txt或者csv文件等),每行代表一条数据,现在希望能合并成 1 个文本文件,且需要去除重复行。分析:一向奉行简单原则,如无必要,绝不复杂。如果数据量不大,那么如下两条命令就可以搞定合并:cat a.txt >> new.txtcat b.txt >> new.txt……去重:cat new...._python 超大文本合并

支付宝小程序iOS端过渡页DFLoadingPageRootController分析_类似支付宝页面过度加载页-程序员宅基地

文章浏览阅读489次。这个过渡页是第一次打开小程序展示的,点击某个小程序前把手机的开发者->network link conditioner->enable & very bad network 就会在停在此页。比如《支付宝运动》这个小程序先看这个类的.h可以看到它继承于DTViewController点击左上角返回的方法- (void)back;#import "DTViewController.h"#import "APBaseLoadingV..._类似支付宝页面过度加载页