FPGA面试真题解析_fpga二进制编码为啥用较多组合逻辑-程序员宅基地

FPGA面试真题解析

1、1、 十进制46.25对应的二进制表达式为( )。(硬件逻辑实习岗)

A 101110.11 B 101101.01 C 101110.1 D 101110.01

解析:

这个问题看上去很简单,那是因为我们平时可以打开电脑上的计算器,然后用程

序员功能立刻就能出结果,但是笔试的时候我们并不能使用这种“作弊“的功能,所以还是要会手算。可能很多同学数电是大一大二时学习的,很久没有接触过这么基础的问题了,那就让我们一起来回忆下吧。

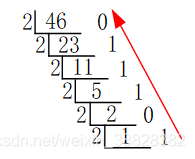

首先这个题目是由整数部分和小数不同共同组成的,整数部分的计算是最简单的,整数部分除以2得到的余数按照逆向顺序排列后就是整数部分转化为二进制后的结果,详细过程如下所示:

46转化为二进制的结果就是101110

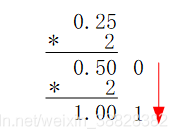

小数部分的计算可能很多人记不清楚了,小数部分每次乘以2后得出的结果取其整数部分,直到小数部分为0或达到精度要求为止,详细过程如下所示:

0.25转化为二进制的结果就是.01

综上所述,最后的答案选择D 101110.01

2、2、 在时序电路的状态转换表中,若状态数N=3,则状态变量数最少为( ) (硬件逻辑实习岗)

A 4 B 8 C 2 D 16

解析:

让我们先看一下一个完整的状态机代码都有哪些内容

//---------------------------------

01 module simple_fsm(

02 input wire sys_clk , //系统时钟50Mh

03 input wire sys_rst_n , //全局复位

04 input wire pi_money , //投币方式可以为:不投币(0)、投1元(1)

05

06 output reg po_cola //po_colaΪ1ʱ֣po_colaΪ0ʱ֠

07 );

08

09 //只有三种状态,使用独热码

10 parameter IDLE = 3’b001;

11 parameter ONE = 3’b010;

12 parameter TWO = 3’b100;

13

14 reg [2:0] state;

15

16 //第一段状态机,描述state跳转,用case

17 always@(posedge sys_clk or negedge sys_rst_n)

18 if(sys_rst_n == 1’b0)

19 state <= IDLE;

20 else case(state)

21 IDLE : if(pi_money == 1’b1) //判断输入情况

22 state <= ONE;

23 else

24 state <= IDLE;

25

26 ONE : if(pi_money == 1’b1)

27 state <= TWO;

28 else

29 state <= ONE;

30

31 TWO : if(pi_money == 1’b1)

32 state <= IDLE;

33 else

34 state <= TWO;

35

36 default : state <= IDLE;

37 endcase

38

39 //第二段状态机,描述state如何影响po_cola输出

40 always@(posedge sys_clk or negedge sys_rst_n)

41 if(sys_rst_n == 1’b0)

42 po_cola <= 1’b0;

43 else if((state == TWO) && (pi_money == 1’b1))

44 po_cola <= 1’b1;

45 else

46 po_cola <= 1’b0;

47

48 endmodule

//---------------------------------

上面是一个用Verilog描述的简单状态机,其功能是每次只能输入1元硬币,输入3元时出可乐,其中01-07行是端口列表部分,10-12行是状态编码部分,14行是定义的状态变量,17-37行是第一段状态机部分,40-46是第二段状态机部分。

题目中说状态数有3个,状态变量数最少为多少(此处应该是指位宽)?上面的例子中10-12行是状态编码,即有多少个状态数就需要有多少个状态编码,这里一共有3种;14行是状态变量,这里为什么状态变量的位宽是3呢?因为我们采用了独热码的编码方式,每个状态数只有1比特为1,其余比特都为0,所以3个状态就要用3位宽的变量,如果是4个状态那就要用4位宽的变量,也就是一共有几个状态数就需要几位宽的状态变量。而题目中说的是“最少“,那么除了我们用独热码的方式对状态进行编码,还有其他的方法吗?答案是当然。我们还可以采用二进制码或格雷码的方式对状态进行编码,上面的例子中如果我们用二进制码编码3个状态则为:2‘b00,2‘b01,2‘b10;而用格雷码编码3个状态则为:2‘b00,2‘b01,2‘b11,都只需要2位宽的状态变量即可,即便是有4个状态数,我们使用2位宽的状态变量依然可以解决问题,要比独热码更节省状态变量的位宽个数。所以这里答案选择C 2。

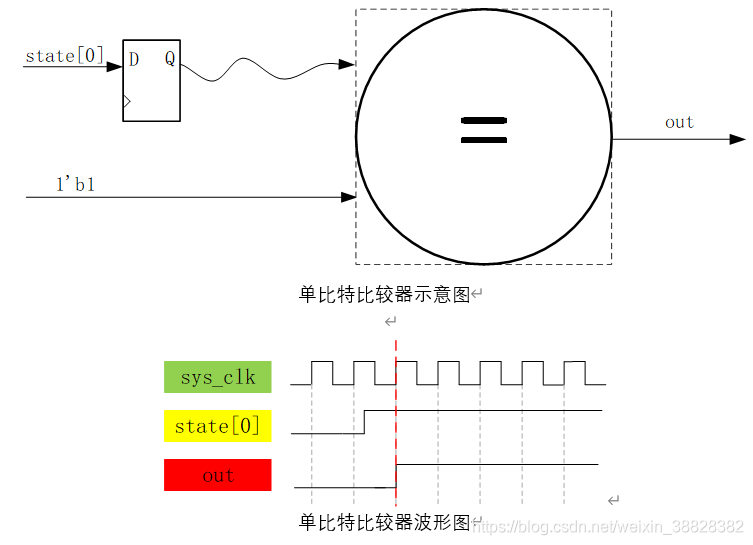

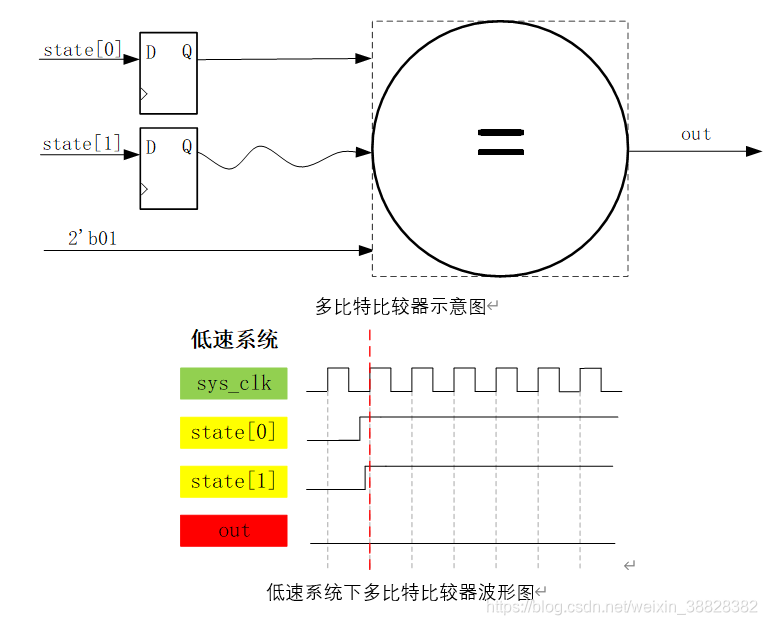

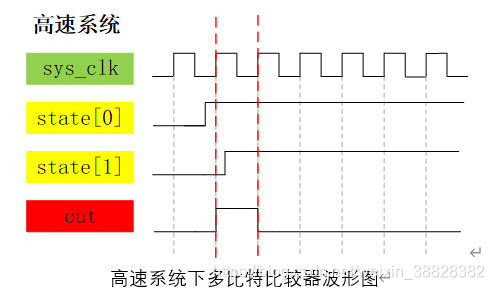

讲到这里并没有结束,我们稍微拓展一下让大家学到更多。为什么例子中我们使用的是独热码而非二进制码或格雷码呢?那就要从每种编码的特性上说起了,首先独热码因为每个状态只有1bit是不同的,所以在执行到43行时的(state == TWO)这条语句时,综合器会识别出这是一个比较器,而因为只有1比特为1,所以综合器会进行智能优化为(state[2] == 1’b1),这就相当于把之前3比特的比较器变为了1比特的比较器,大大节省了组合逻辑资源,但是付出的代价就是状态变量的位宽需要的比较多,而我们FPGA中组合逻辑资源相对较少,所以比较宝贵,而寄存器资源较多,所以很完美。而二进制编码的情况和独热码刚好相反,他因为使用了较少的状态变量,使之在减少了寄存器状态的同时无法进行比较器部分的优化,所以使用的寄存器资源较少,而使用的组合逻辑资源较多,我们还知道CPLD就是一个组合逻辑资源多而寄存器逻辑资源少的器件,因为这里我们使用的是FPGA器件,所以使用独热码进行编码。就因为这个比较部分的优化,还使得使用独热码编码的状态机可以在高速系统上运行,其原因是多比特的比较器每个比特到达比较器的时间可能会因为布局布线的走线长短而导致路径延时的不同,这样在高速系统下,就会导致采集到不稳定的状态,导致比较后的结果产生一个时钟的毛刺,使输出不稳定,而单比特的比较器就不用考虑这种问题。下面是示意图解析。

用独热码编码虽然好处多多,但是如果状态数非常多的话即使是FPGA也吃不消独热码对寄存器的消耗,所以当状态数特别多的时候可以使用格雷码对状态进行编码。格雷码虽然也是和二进制编码一样使用的寄存器资源少,组合逻辑资源多,但是其相邻状态转换时只有一个状态发生翻转,这样不仅能消除状态转换时由多条信号线的传输延迟所造成的毛刺,又可以降低功耗,所以要优于二进制编码的方式,相当于是独热码和二进制编码的折中。

最后我们用一个表格来总结一下什么时候使用什么方式的编码效果最好 (有时候不管你使用哪种编码方式,综合器会根据实际情况在综合时智能的给你进行编码的转换,当然这需要你设置额外的综合约束,这里我们不再详细讲解) 。

3、3、 只读存储器ROM中的内容,当电源断掉后又接通,存储器中的内容 ( )。(硬件逻辑实习岗)

A 全部为0 B不可预料 C 保持不变 D 全部改变

解析:考察数字电路中存储器的基本知识

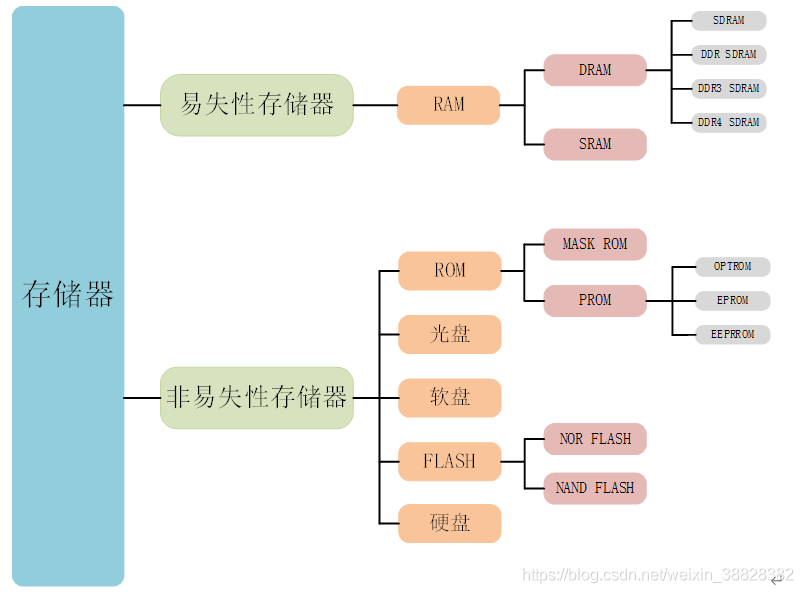

下图所示为常见存储器件的性质关系

一、易失性存储器的代表就是RAM,RAM又分为DRAM(动态随机存储器)和SRAM(静态随机存储器),它们之间主要在于生产工艺不同。

SRAM保存数据是通过晶体管进行锁存的,其工艺复杂,生产成本高,所以价格相对较贵,不易做大容量,但是速度更快;DRAM保存数据靠电容充电来维持容量,生产成本较SRAM低,所以价格相对便宜,容量可以做到很大,速度虽然不如SRAM快但是随着工艺技术的提升,速度也很可观,所以较为常用。DRAM和SRAM都是异步通信的,速率没有SDRAM(同步动态随机存储器)和SSRAM(同步静态随机存储器)快。所以现在大容量RAM存储器是选用SDRAM的。

CPU中的Cache实质属于SRAM,而内存条则是属于DRAM。SDRAM和DDR SDRAM的区别在于DDR(Double Data Rate)是双倍速率。SDRAM只在时钟的上升沿表示一个数据,而DDR SDRAM能在上升沿和下降沿都表示一个数据。DDR也一步步经过改良出现了一代、二代、三代、四代,以及低功耗版本,现在也有五代。

二、 非易失性存储器常见的有ROM,FLASH,光盘,软盘,硬盘。他们作用相同,只是实现工艺不一样。

ROM(Read Only Memory)在以前就是只读存储器,就是说这种存储器只能读取它里面的数据无法向里面写数据。实际是以前向存储器写数据不容易,所以这种存储器就是厂家造好了写入数据,后面不能再次修改。现在技术成熟了,ROM也可以写数据,但是名字保留了下来。ROM分为MASK ROM、OTPROM、EPROM、EEPROM。MASK ROM是掩膜ROM这种ROM是一旦厂家生产出来,使用者无法再更改里面的数据。OTPROM(One Time Programable ROM)一次可变成存储器,出厂后用户只能写一次数据,然后再也不能修改了,一般做存储密钥。EPROM(Easerable Programable ROM)这种存储器就可以多次擦除然后多次写入了。但是要在特定环境紫外线下擦除,所以这种存储器也不方便写入。EEPROM(Eelectrically Easerable Programable ROM)电可擦除ROM,现在使用的比较多因为只要有电就可擦除数据,就可以写入数据。

FLASH是一种可以写入和读取的存储器,叫闪存,FLASH也叫FLASH ROM,有人把FLASH当做ROM。FLASH和EEPROM相比,FLASH的存储容量大。FLASH的速度比现在的机械硬盘速度快,现在的U盘和SSD固态硬盘都是Nandflash。FLASH又分为Norflash和Nandflash。

综上所述,本题答案选C 保持不变

4、4、 在Verilog语言中,a = 4’b1011,那么&a为( )。(硬件逻辑实习岗)

A 4’b1111 B 1’b1 C 1’b0 D 4’b1011

解析:考察Verilog基本语法中的操作符

“&”操作符有两种用途,既可以作为一元操作符(仅有一个操作数),也可以作为二元操作符(有两个操作数)。

当“&”作为一元操作符时表示归约与。&m是将m中所有比特相与,最后的结果为1bit。例:&4‘b1111 = 1&1&1&1 = 1’b1,&4’b1101 = 1&1&0&1 = 1’b0。

当“&”作为二元操作符时表示按位与。m&n是将m的每个比特与n的相应比特相与,在运算的时候要保证m和n的比特数相等,最后的结果和m(n)的比特数相同。例:4’b1010&4’b0101 = 4’b0000,4’b1101&4’b1111 = 4’b1101。

我们在写Verilog代码时常常当if的条件有多个同时满足时就执行使用“&&”逻辑与操作符。m &&n是判断m和n是否都为真,最后的结果只有1bit,如果都为真则输出1‘b1,如果不都为真则输出1’b0。要注意和“&”的功能区分。

此外“&”操作符作为归约与使用时还有妙用。下面是一个分频器,代码结构简单,逻辑也不复杂,就是当计数器计数到15时让输出out取反,相当于实现对sclk的32分频。

//---------------------------------

01 module divider(

02 input wire sclk ,

03 input wire rst_n ,

04

05 output reg out

06 );

07

08 reg [3:0] cnt;

09

10 //cnt

11 always@(posedge sclk or negedge rst_n)

12 if(rst_n == 1’b0)

13 cnt <= 4’b0;

14 else if(cnt == 4’d15)

15 cnt <= 4’b0;

16 else

17 cnt <= cnt + 1’b1;

18

19 //out

20 always@(posedge sclk or negedge rst_n)

21 if(rst_n == 1’b0)

22 out <= 1’b0;

23 else if(cnt == 4’d15)

24 out <= ~out;

25

26 endmodule

//---------------------------------

我们可以看到第14行和低23行都使用了一个判断语句,是判断计数器cnt是否达到15,如果达到是计数器清零,且输出out取反。我们比较器要将cnt的每一个比特都和4‘d15的每一位进行比较,也就是判断(cnt == 4’b1111),会浪费更多的资源。而我们今天想到了“&”的用法就可以实现妙用,我们将判断条件改为(&cnt == 1‘b1),当计数器计数到15时,即所有的比特都为变为了1,那么&cnt为1‘b1,而其余情况&cnt都为1’b0,这样比较的位数就只有1位了,节省了资源。希望大家以后遇到此类相关情况推荐使用“&cnt”的方法。

注:如果大家在使用QuartusII工具进行验证上面的结论,想看看是否真的会节约逻辑资源时,可能看不到想要的结果,这是因为当描述的系统不复杂时综合器能够比较好的对逻辑进行优化(证明被优化的结果可以通过RTL视图定位在Chip Planner中的位置得到验证),而当描述的系统较为复杂时就不能够保证综合器能够有比较好的优化效果,或许以后综合器可以变得更加智能,但是目前还是使用推荐的写法更稳妥。

综上所述,本题答案选C 1‘b0

智能推荐

2022黑龙江最新建筑八大员(材料员)模拟考试试题及答案_料账的试题-程序员宅基地

文章浏览阅读529次。百分百题库提供建筑八大员(材料员)考试试题、建筑八大员(材料员)考试预测题、建筑八大员(材料员)考试真题、建筑八大员(材料员)证考试题库等,提供在线做题刷题,在线模拟考试,助你考试轻松过关。310项目经理部应编制机械设备使用计划并报()审批。A监理单位B企业C建设单位D租赁单位答案:B311对技术开发、新技术和新工艺应用等情况进行的分析和评价属于()。A人力资源管理考核B材料管理考核C机械设备管理考核D技术管理考核答案:D312建筑垃圾和渣土._料账的试题

chatgpt赋能python:Python自动打开浏览器的技巧-程序员宅基地

文章浏览阅读614次。本文由chatgpt生成,文章没有在chatgpt生成的基础上进行任何的修改。以上只是chatgpt能力的冰山一角。作为通用的Aigc大模型,只是展现它原本的实力。对于颠覆工作方式的ChatGPT,应该选择拥抱而不是抗拒,未来属于“会用”AI的人。AI职场汇报智能办公文案写作效率提升教程 专注于AI+职场+办公方向。下图是课程的整体大纲下图是AI职场汇报智能办公文案写作效率提升教程中用到的ai工具。_python自动打开浏览器

Linux中安装JDK-RPM_linux 安装jdk rpm-程序员宅基地

文章浏览阅读545次。Linux中安装JDK-RPM方式_linux 安装jdk rpm

net高校志愿者管理系统-73371,计算机毕业设计(上万套实战教程,赠送源码)-程序员宅基地

文章浏览阅读25次。免费领取项目源码,请关注赞收藏并私信博主,谢谢-高校志愿者管理系统主要功能模块包括页、个人资料(个人信息。修改密码)、公共管理(轮播图、系统公告)、用户管理(管理员、志愿用户)、信息管理(志愿资讯、资讯分类)、活动分类、志愿活动、报名信息、活动心得、留言反馈,采取面对对象的开发模式进行软件的开发和硬体的架设,能很好的满足实际使用的需求,完善了对应的软体架设以及程序编码的工作,采取SQL Server 作为后台数据的主要存储单元,采用Asp.Net技术进行业务系统的编码及其开发,实现了本系统的全部功能。

小米宣布用鸿蒙了吗,小米OV对于是否采用鸿蒙保持沉默,原因是中国制造需要它们...-程序员宅基地

文章浏览阅读122次。原标题:小米OV对于是否采用鸿蒙保持沉默,原因是中国制造需要它们目前华为已开始对鸿蒙系统大规模宣传,不过中国手机四强中的另外三家小米、OPPO、vivo对于是否采用鸿蒙系统保持沉默,甚至OPPO还因此而闹出了一些风波,对此柏铭科技认为这是因为中国制造当下需要小米OV几家继续将手机出口至海外市场。 2020年中国制造支持中国经济渡过了艰难的一年,这一年中国进出口贸易额保持稳步增长的势头,成为全球唯一..._小米宣布用鸿蒙系统

Kafka Eagle_kafka eagle git-程序员宅基地

文章浏览阅读1.3k次。1.Kafka Eagle实现kafka消息监控的代码细节是什么?2.Kafka owner的组成规则是什么?3.怎样使用SQL进行kafka数据预览?4.Kafka Eagle是否支持多集群监控?1.概述在《Kafka 消息监控 - Kafka Eagle》一文中,简单的介绍了 Kafka Eagle这款监控工具的作用,截图预览,以及使用详情。今天_kafka eagle git

随便推点

Eva.js是什么(互动小游戏开发)-程序员宅基地

文章浏览阅读1.1k次,点赞29次,收藏19次。Eva.js 是一个专注于开发互动游戏项目的前端游戏引擎。:Eva.js 提供开箱即用的游戏组件供开发人员立即使用。是的,它简单而优雅!:Eva.js 由高效的运行时和渲染管道 (Pixi.JS) 提供支持,这使得释放设备的全部潜力成为可能。:得益于 ECS(实体-组件-系统)架构,你可以通过高度可定制的 API 扩展您的需求。唯一的限制是你的想象力!_eva.js

OC学习笔记-Objective-C概述和特点_objective-c特点及应用领域-程序员宅基地

文章浏览阅读1k次。Objective-C概述Objective-C是一种面向对象的计算机语言,1980年代初布莱德.考斯特在其公司Stepstone发明Objective-C,该语言是基于SmallTalk-80。1988年NeXT公司发布了OC,他的开发环境和类库叫NEXTSTEP, 1994年NExt与Sun公司发布了标准的NEXTSTEP系统,取名openStep。1996_objective-c特点及应用领域

STM32学习笔记6:TIM基本介绍_stm32 tim寄存器详解-程序员宅基地

文章浏览阅读955次,点赞20次,收藏16次。TIM(Timer)定时器定时器可以对输入的时钟进行计数,并在计数值达到设定值时触发中断16位计数器、预分频器、自动重装寄存器的时基单元,在 72MHz 计数时钟下可以实现最大 59.65s 的定时,59.65s65536×65536×172MHz59.65s65536×65536×721MHz不仅具备基本的定时中断功能,而且还包含内外时钟源选择、输入捕获、输出比较、编码器接口、主从触发模式等多种功能。_stm32 tim寄存器详解

前端基础语言HTML、CSS 和 JavaScript 学习指南_艾编程学习资料-程序员宅基地

文章浏览阅读1.5k次。对于任何有兴趣学习前端 Web 开发的人来说,了解 HTML、CSS 和JavaScript 之间的区别至关重要。这三种前端语言都是您访问过的每个网站的用户界面构建块。而且,虽然每种语言都有不同的功能重点,但它们都可以共同创建令人兴奋的交互式网站,让用户保持参与。因此,您会发现学习所有三种语言都很重要。如果您有兴趣从事前端开发工作,可以通过多种方式学习这些语言——在艾编程就可以参与到学习当中来。在本文中,我们将回顾每种语言的特征、它们如何协同工作以及您可以在哪里学习它们。HTML vs C._艾编程学习资料

三维重构(10):PCL点云配准_局部点云与全局点云配准-程序员宅基地

文章浏览阅读2.8k次。点云配准主要针对点云的:不完整、旋转错位、平移错位。因此要得到完整点云就需要对局部点云进行配准。为了得到被测物体的完整数据模型,需要确定一个合适的坐标系变换,将从各个视角得到的点集合并到一个统一的坐标系下形成一个完整的数据点云,然后就可以方便地进行可视化,这就是点云数据的配准。点云配准技术通过计算机技术和统计学规律,通过计算机计算两个点云之间的错位,也就是把在不同的坐标系下的得到的点云进行坐标变..._局部点云与全局点云配准

python零基础学习书-Python零基础到进阶必读的书藉:Python学习手册pdf免费下载-程序员宅基地

文章浏览阅读273次。提取码:0oorGoogle和YouTube由于Python的高可适应性、易于维护以及适合于快速开发而采用它。如果你想要编写高质量、高效的并且易于与其他语言和工具集成的代码,《Python学习手册:第4 版》将帮助你使用Python快速实现这一点,不管你是编程新手还是Python初学者。本书是易于掌握和自学的教程,根据作者Python专家Mark Lutz的著名培训课程编写而成。《Python学习..._零基础学pythonpdf电子书