MAX1167和MAX1168数据采集芯片_max1167采样率算法-程序员宅基地

MAX1167和MAX1168数据采集芯片

1 描述

MAX1167/MAX1168为低功耗、多通道、16位逐次逼近型模数转换器(ADC),具有集成的+4.096V基准电压、1个基准电压缓冲器、一个内部振荡器和自动关断等特点,并带有一个高速SPI/QSPI/兼容MICROWIRE的接口。MAX1167/MAX1168采用单+5V模拟电源工作,且具有独立的数字电源,允许直接与+2.7V至+5.5V的数字逻辑接口。

MAX1167/MAX1168功耗低。采用外部基准电压、工作采样速率为200ksps时,MAX1167/MAX1168的功耗仅为3.6mA (AVDD = DVDD = +5V)。在10ksps时,自动掉电功能将电源电流降到185µA,在更低采样速率下,功耗可低至10µA以下。

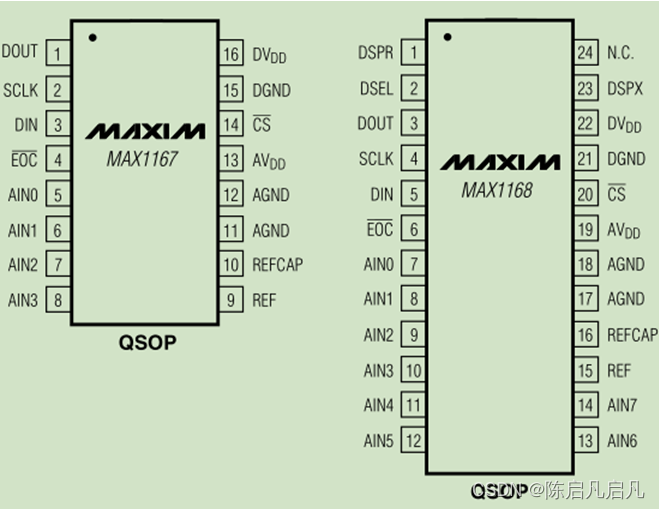

MAX1167有一个4通道的模拟输入多路复用器,MAX1168有一个8通道的模拟输入多路复用器。另外,MAX1168具有DSP帧同步输入和输出,它简化了数字信号处理器(DSP)启动的转换。MAX1168包括一个数据位宽选择输入,用于选择8位位宽或16位位宽模式。两个器件都具有扫描模式,可以顺序转换各个通道或连续转换某一个通道。

动态性能及低功耗,结合易于使用和内置基准等特性,使MAX1167/MAX1168尤其适合于控制和数据采集,或其它对功耗和尺寸要求严格的应用。MAX1167采用16引脚QSOP封装,MAX1168采用24引脚QSOP封装。两个器件均保证工作在整个商业级(0°C至+70°C)和扩展工业级(-40°C至+85°C)温度范围。利用MAX1168评估板可对MAX1168进行评估。

2 主要特征

-

16位分辨率,无误码 - +5V单电源工作

-

可调的逻辑电平(+2.7V至+5.25V) -

输入电压范围:0至VREF -

内部(+4.096V)或外置基准(+3.8V至AVDD) -

内部采样/保持,4MHz输入带宽 -

内部或外部时钟 -

SPI/QSPI/MICROWIRE兼容的串行接口,MAX1168能够完成DSP启动的转换 -

8位位宽或16位位宽数据输出模式(仅MAX1168) -

4通道(MAX1167)或8通道(MAX1168)输入复用器 -

扫描模式顺序转换多个 -

通道或连续转换单个通道 -

低功耗 -

200ksps时,3.6mA -

100ksps时,1.85mA -

10ksps时,185µA -

0.6µA的完全关断模式 -

小型封装尺寸 -

16引脚QSOP封装(MAX1167) -

24引脚QSOP封装(MAX1168)

3 应用/用途

- 加速计测量

- 数据采集系统

- 工业I/O模块

- 工业过程控制

- 电机控制

- 热电偶测量

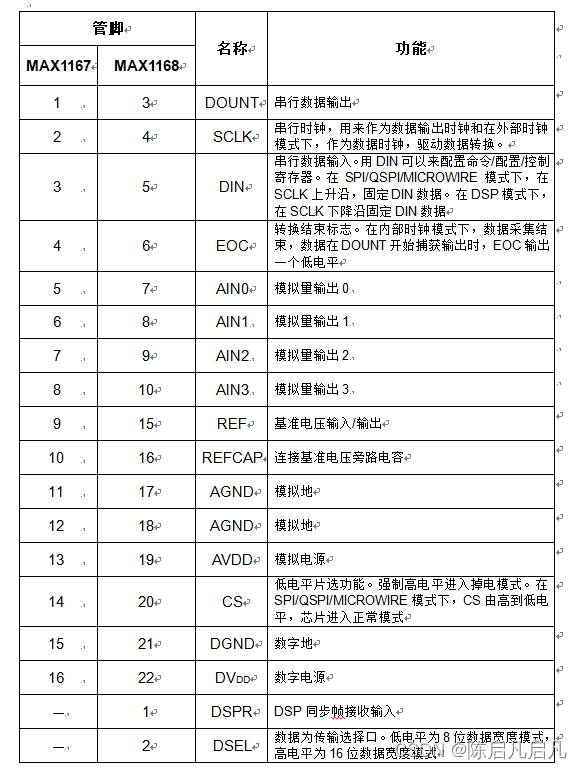

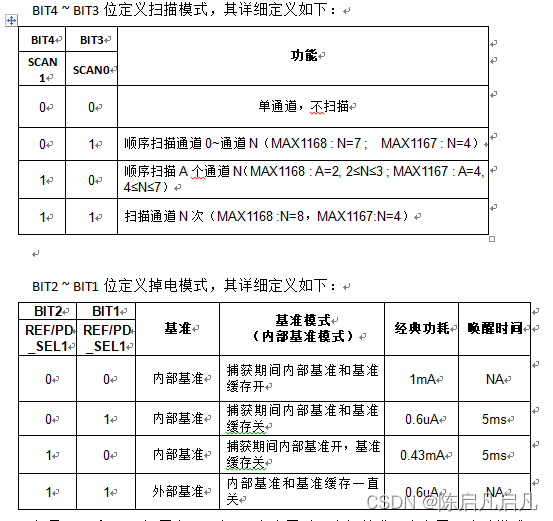

4 管脚定义

如果bit2和bit1设置为0,当CS高电平时,内部基准一直为开,这种模式有最快的开启时间。

如果bit2=0和bit1=1,则在CS上升沿,内部基准和基准缓存均关闭,这种模式下,功耗最低。在SPI/QSPI模式下,内部基准和基准缓存CS下降沿被唤醒。

如果bit2=1和bit1=0,则在CS上升沿,内部基准一直开,内部缓存关闭。在CS上升沿进入这种模式。在CS下降沿,内部缓存被唤醒。

如果bit2=1和bit1=1,关闭内部基准和内部缓存,以允许连接一个外部基准。使用外部基准时,没有额外的唤醒时间。

5.3 操作模式

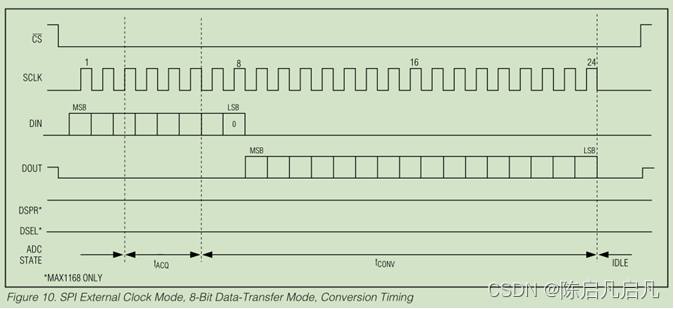

5.3.1 外部时钟8位数据转换模式

CS下降沿唤醒模拟电路以及允许时钟计时数据。当在4.8MHZ(最大时钟)时钟下运行时,确保时钟占空比在45%~55%之间。在低时钟频率下运行时,确保高、低电平至少有93ns的持续时间。在外部时钟低至125KHZ时,由于采样电容的泄露,会降低采样精度。CS低电平后,Dout由高阻态进入低电平。输入数据在SCLK的上升沿锁定。

在SCLK的第一个上升沿,输入数据开始从Din脚加载到命令/配置/控制寄存器中。在SCLK的第3个上升沿,设备选择相应通道捕获数据,在SCLK第6个下降沿,数据捕获结束,开始采样和数据转换。在第8个上升沿,设置和配置完成。在第8个下降沿,转换结果在Dout开始有效输出。要读取整个转换结果,需要16个时钟。在转换结果全部输出后,CS上升沿之前,如果有额外的时钟脉冲,此时,Dout上的值为0。在外部时钟8位数据传输模式下,共需要24个时钟才能完成。

转换结束过,强制CS为高,为了最大吞吐量,在指定的最小间隔时间(t CSW)后,立即拉低CS可使设备进入下一次转换初始化状态。在转换过程中,强制CS为高,会禁止转换,并进入掉电模式。

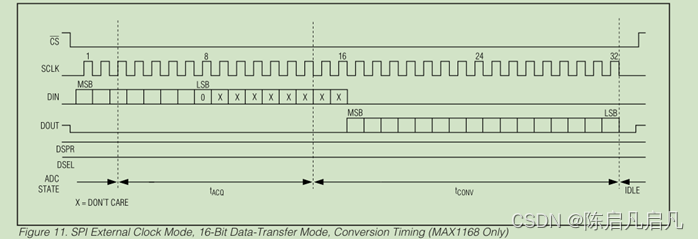

5.3.2 外部时钟,16位数据模式

CS下降沿唤醒模拟电路以及允许时钟计时数据。当在4.8MHZ(最大时钟)时钟下运行时,确保时钟占空比在45%~55%之间。在低时钟频率下运行时,确保高、低电平至少有93ns的持续时间。在外部时钟低至125KHZ时,由于采样电容的泄露,会降低采样精度。CS低电平后,Dout由高阻态进入低电平。输入数据在SCLK的上升沿锁定。

在SCLK的第一个上升沿,输入数据开始从Din脚加载到命令/配置/控制寄存器中。在SCLK的第3个上升沿,设备选择相应通道捕获数据,在第8个上升沿,设置和配置完成。在SCLK第14个下降沿,数据捕获结束,开始采样和数据转换。在第16个下降沿,转换结果在Dout开始有效输出。要读取整个转换结果,需要16个时钟。在转换结果全部输出后,CS上升沿之前,如果有额外的时钟脉冲,此时,Dout上的值为0。在外部时钟16位数据传输模式下,共需要32个时钟才能完成。

转换结束过,强制CS为高,为了最大吞吐量,在指定的最小间隔时间(t CSW)后,立即拉低CS可使设备进入下一次转换初始化状态。在转换过程中,强制CS为高,会种植转换,并进入掉电模式。

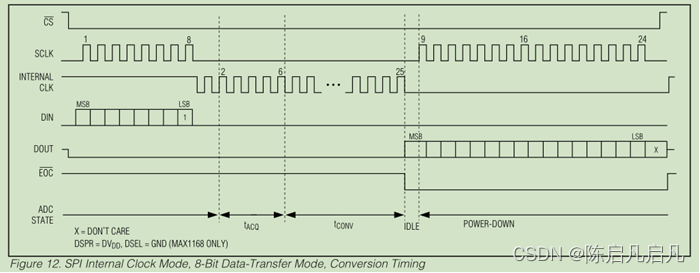

5.3.3 内部时钟模式8为数据转换模式

CS下降沿唤醒模拟电路以及允许时钟计时数据。当在4.8MHZ(最大时钟)时钟下运行时,确保时钟占空比在45%~55%之间。在低时钟频率下运行时,确保高、低电平至少有93ns的持续时间。在外部时钟低至125KHZ时,由于采样电容的泄露,会降低采样精度。CS低电平后,Dout由高阻态进入低电平。输入数据在SCLK的上升沿锁定。

在SCLK的第一个上升沿,输入数据开始从Din脚加载到命令/配置/控制寄存器中。在SCLK的第3个上升沿,设备选择相应通道捕获数据,在第8个上升沿,设置和配置完成。在第8个上升沿后125ns,内部时钟被激活。内部时钟开启同时外部时钟关闭,在捕获期间,关闭外部时钟时钟可获得最低的噪声。捕获开始于内部时钟的第2个上升沿,结束于内部时钟的第6个下降沿。转换结果开始有效后,每一位移入内存中,在EOC的下降沿,转换结果有效输出。在EOC的下降沿,内部振荡器和模拟电路关闭。EOC下降沿可作为重启外部时钟的信号。要读取整个转换结果,需要16个时钟。在转换结果全部输出,CS上升沿之前,如果有额外的时钟脉冲,此时,Dout上的值为0。在内部时钟8位数据传输模式下,共需要24个外部时钟和25个内部时钟才能完成采集。

转换结束过,强制CS为高,为了最大吞吐量,在指定的最小间隔时间(t CSW)后,立即拉低CS可使设备进入下一次转换初始化状态。在转换过程中,强制CS为高,会种植转换,并进入掉电模式。在EOC下降沿,重启外部时钟。

转换结束过,强制CS为高,为了最大吞吐量,在指定的最小间隔时间(t CSW)后,立即拉低CS可使设备进入下一次转换初始化状态。在转换过程中,强制CS为高,会种植转换,并进入掉电模式。

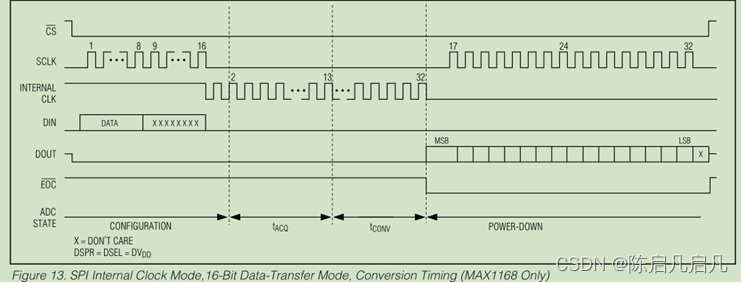

5.3.4 内部时钟,16为数据转换模式

其与内部时钟,8位数据转换模式相似,不同之处请看图

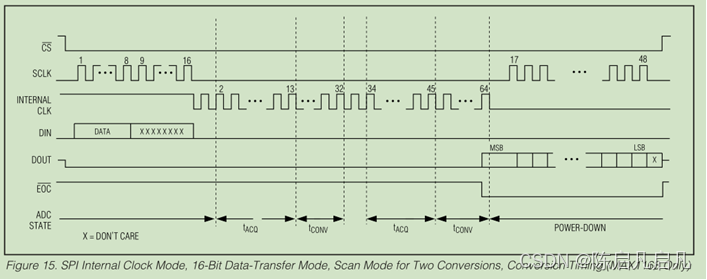

5.3.5 内部时钟,16位转换模式,扫描模式

MAX1168扫描模式允许多个通道被连续扫描或者单个通道被扫描8次。仅在内部时钟模式下,可使能扫描模式。

智能推荐

Centos7搭建hadoop的错误(datanode)和(nodeManager)没启动的解决方法_hadoop集群部署时datenode,nodemanger-程序员宅基地

文章浏览阅读3.1k次,点赞4次,收藏14次。1.datanode没有启动,就要到slaves节点去找错误。解决方法:前提是配置文档没错,删除datanode的格式化信息,再重新格式化#注意:在datanode节点上删除[hadoop@node2 ~]$ cd /home/hadoop/dfs/data/current[hadoop@node2 current]$rm VERSION[hadoop@node3 ~]$ cd ..._hadoop集群部署时datenode,nodemanger

安卓-ListView基本使用_使用listview需要下载什么软件吗-程序员宅基地

文章浏览阅读1k次。今天的目标是使用ListView控件完成一个布局,左边一个图标,右边分为上线两部分:标题和内容;ListView在使用时要考虑内存优化,就是使用ViewHolder(自己定义的一个内部类,存储布局中的控件的索引)适配器使用继承自ArrayAdapter的适配器,也可以继承自BaseAdapter(要多写几个方法)目前虽然还有公司在使用,但是后面大家陆续都会转向RecyclerView,_使用listview需要下载什么软件吗

摩斯密码_摩斯密码是通用的吗-程序员宅基地

文章浏览阅读1.6k次。摩斯密码_摩斯密码是通用的吗

物联网架构-程序员宅基地

文章浏览阅读797次,点赞13次,收藏18次。物联网架构。

已安装对应模块,但报无法找到模块“XXX”的声明文件的解决方案_找不到模块“qs”或其相应的类型声明-程序员宅基地

文章浏览阅读1.7k次。在一次做项目的时候,我封装一个axios的文件,想引入qs组件,因为axios已经自带qs组件了,所以直接。好了,工作忙,不吹了,直接在src文件目录下创建一个 shime-vue.d.ts文件,在里面写入。但是,它居然给我报了如下的提示(这张图片是我写博客的时候找的类似的一张图片,当成qs就好)保存,就可以了,qs可以正常引入了,不会再报找不到模块了。_找不到模块“qs”或其相应的类型声明

C# 静态代码块(静态构造函数)_java static块 c#-程序员宅基地

文章浏览阅读1.2w次。本来以为是和java一样写法。结果找了半天也没找到。原来有静态构造函数一样的功能。class SimpleClass{ // Static constructor static SimpleClass() { //... }}静态构造函数具有以下特点:静态构造函数既没有访问修饰符,也没有参数_java static块 c#

随便推点

Web安全工具大集合-程序员宅基地

文章浏览阅读4.3k次。Test sites / testing groundsSPI Dynamics (live) – http://zero.webappsecurity.com/Cenzic (live) – http://crackme.cenzic.com/Watchfire (live) – http://demo.testfire.net/Acunetix (live) – http:

MySQL开发技巧 - 分页和索引_本关任务:能分页读取表中数据,针对大数据量进行简单优化。-程序员宅基地

文章浏览阅读2.6k次,点赞2次,收藏3次。第1关:MySQL 分页查询本关任务:能分页读取表中数据,针对大数据量进行简单优化。USE Products;#请在此处添加实现代码########## Begin ###########1.分页查询select prod_id from products limit 5,5;#2.用子查询优化分页查询语句select prod_id from products where prod_id >=(select prod_id from products limit 10,1) l_本关任务:能分页读取表中数据,针对大数据量进行简单优化。

WPF 控件专题 Image控件详解_wpf image-程序员宅基地

文章浏览阅读5.3k次。WPF 控件专题 Image控件详解_wpf image

OMPL库学习笔记0--写在前面_ompl time-程序员宅基地

文章浏览阅读2.7k次。 从今天开始学习OMPL库函数,自己是一个没有恒心的人,而OMPL库又实在比较庞大,这算是写在前面的自我鼓励吧。记录这些学习笔记是自我加深认识的一个过程,肯定存在许多错误,希望有看到错误的小伙伴可以不吝指教,也希望可以和大家多多交流,相互学习。 在了解OMPL库之前还有一步是必须的,那就是下载OMPL库,就像我们看一本书,你总得先有这本书吧 我自己在网上找了一..._ompl time

PMP之项目风险管理---实施定量风险分析_pmp敏感性分析-程序员宅基地

文章浏览阅读2.3k次。1. 气泡图_pmp敏感性分析

时序分析的基本概念和术语-程序员宅基地

文章浏览阅读3.4k次,点赞11次,收藏45次。一、发起沿和捕获沿发起沿:数据发送的时钟沿叫发起沿。捕获沿:数据接收的时钟沿叫捕获沿。发起沿和捕获沿之间一般情况下相差一个时钟周期。二、四种时序路径模型1.外部输入端口到内部寄存器的路径。2.内部寄存器之间的时序路径。3.内部寄存器到外部端口的时序路径。4.输入到输出的组合路径。上述四种时序路径的起点和终点start end point1.Device A/clk rega/D2.rega/clk regb/D_时序