基于QuartusII的简易CPU设计,在目标机器上成功运行,新手学习入门有良好的参考意义。

”基于QuartusII的CPU设计“ 的搜索结果

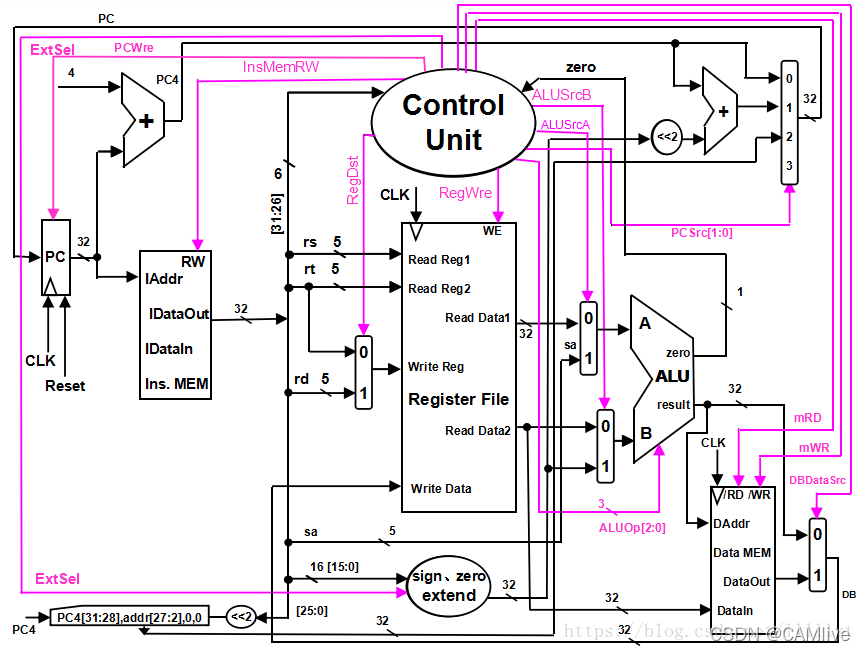

VHDL单周期CPU设计,基于Quartus II 开发平台

微指令实现模型机的操作的关键在于整个模型机的运行(主要体现在各种算术运算和逻辑运算上)是有顺序和步骤(“周期”或者说是“节拍”)的,...能够真正通过自己动手设计一个底层元件,进而实现一个简易 CPU 运算器。

CPU是广泛使用的串行数据通讯电路。本设计包含发送器、接收器和波特率发生器。...本文利用Quartus Ⅱ软件仿真环境,基于FPGA(现场可编程门阵列)/CPLD(复杂可编程逻辑器件)设计与实现16位CPU的设计方案。

16位

32位CPU-Quartus代码完整版

简单的CPU设计,采用QuartusⅡ软件实现。压缩包中有每个元件的设计,也有最终的CPU(压缩包中名为middle)

基于quartus的计算机核心设计 转的,清晰度一般

基于Quartus II的计算机组成与体系结构综合实验教程语音编辑锁定讨论上传视频《基于Quartus II的计算机组成与体系结构综合实验教程》是2011年科学出版出版的图书,作者是杨军。书名基于Quartus II的计算机组成与体系...

1、学习应用移位相加原理设计8位乘法器。 2、了解移位相加原理构成乘法器与用组合逻辑电路直接设计的同样功能的电路优势。 设计方法: 方法一:(用乘号实现乘法) module chengfaqi(a,b,dout); input [7:0] a,...

基于Quartus Prime的NiosII基础开发流程 软件版本:Quartus Prime Standard Edition 18.0 Windows 1. 建立工程 启动Quartus Prime选择New Project Wizard 设置工程名及工作目录 根据提示使用默认配置直到...

换了个地址

74LS192是一种二进制同步上升计数器芯片,可以用于数字计数和时序控制等应用。它是TTL逻辑家族中的一员,采用了低功耗,高噪声抑制特性以及快速反应时间的优点,广泛应用于各种电子设备和系统中。

在 Quartus II 中,设计 CPU 可以采用多种方式实现,其中 IICPU 是一种常见的设计方式。 IICPU 是一种针对 Altera FPGA 的基于指令的CPU架构,其设计精简高效,适合于需要实现软处理器的应用场景。IICPU 的设计基于...

基于EDA技术的单周期CPU设计与实现——计算机组成原理实践语音编辑锁定讨论上传视频《基于EDA技术的单周期CPU设计与实现——计算机组成原理实践》是2012年出版的图书,主要讲述了CPU的设计与实现。书名基于EDA技术的...

以Altera公司的Quartus Ⅱ 7.2作为开发工具,研究了基于FPGA的DDS IP核设计,并给出基于Signal Tap II嵌入式逻辑分析仪的仿真测试结果。将设计的DDS IP核封装成为SOPC Builder自定义的组件,结合32位嵌入式CPU软核...

存储在存储单元中的值决定逻辑单元的逻辑功能,模块之间或模块之间的连接和I/O最终决定了FPGA可以实现的功能,FPGA(场程序器门阵列的程序器设备开发中的产品,开发分号电路,帮助在专用集成电路的研究方向上解决...

整理看[《基于FPGA的嵌入式系统设计 – Altera Soc FPGA 》第二版],整理部分很可能有错误。了解FPGA概念参考:认识FPGA Verilog HDL前3段。

设计好测试用的汇编代码后,然后利用Quartus II软件附带的DebugController编写汇编编译规则。接着,利用DebugController软件把汇编编译之后的二进制代码置入到所采用的存储器中,并对设计好的8位CPU进行测试。

Quartus使用入门及一些实验经验 Maxplus主要是教学使用,对于一般的教学需求,Max...# Quartus II Version 9.0 Build 132 02/25/2009 SJ Full Version # File: E:\code\computer system\cpu design\result\memory\mem...

推荐文章

- 基于手机蓝牙的arduino遥控小车_sumjess-程序员宅基地

- document对象常用的属性和方法_document属性-程序员宅基地

- 【Vue五分钟】五分钟了解vue的常用实例方法_vue实例方法-程序员宅基地

- 关于pytorch膨胀卷积的程序_膨胀卷积的pytorch代码-程序员宅基地

- Insight量子位智库 ✪ AIGC/Al生成内容产业展望报告_量子位《aigc/ai生成内容产业展望报告》-程序员宅基地

- Java多线程异步任务_submitlistenable-程序员宅基地

- 科普帖:什么是IaaS?与SaaS、PaaS有何不同_google drive iaas-程序员宅基地

- 滚动栏范围位置函数(SetScrollRange、SetScrollPos、GetScrollRange、GetScrollPos)-程序员宅基地

- 【Java基础】之AWT,一篇文章搞懂awt(包含绘图)-程序员宅基地

- C++ Primer问题总结(7)_executionpolicy&&-程序员宅基地